El tamaño de un transistor se mide por la anchura de su canal. Los actuales superan los diez nanómetros. Por debajo el rendimiento en conmutación se degrada mucho por efecto túnel entre la fuente y el drenador. El fosforeno promete ser la solución. Este material presenta una masa efectiva anisótropa y según las simulaciones por ordenador permite alcanzar un canal de solo un nanómetro sin degradar el rendimiento en transistores MOSFET y TFET.

El artículo (teórico) es Hesameddin Ilatikhameneh, Tarek Ameen, …, Rajib Rahman, «Saving Moore’s Law Down To 1nm Channels With Anisotropic Effective Mass,» arXiv:1605.03979 [cond-mat.mes-hall].

[PS 21 Ago 2016] El artículo se ha publicado en una revista, Hesameddin Ilatikhameneh et al., «Saving Moore’s Law Down To 1 nm Channels With Anisotropic Effective Mass,» Scientific Reports 6: 31501 (19 Aug 2016), doi: 10.1038/srep31501.

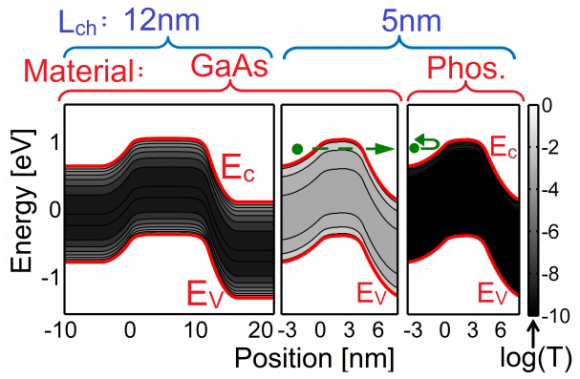

El futuro de los transistores de efecto de campo tipo metal-óxido-semiconductor (MOSFET) y tipo efecto túnel (TFET) parece asociado a los materiales bidimensionales (como el grafeno, fosforeno, siliceno, etc.). La figura ilustra en niveles de gris la probabilidad de efecto túnel a través del canal para un transistor de GaAs cuando se pasa de 12 nm a 5 nm. Para un canal de fosforeno de 5 nm dicha probabilidad es muy pequeña (un color negro intenso).

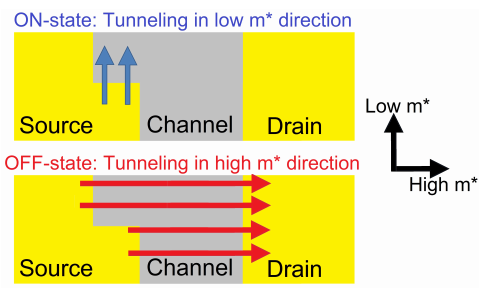

Los electrones se mueven a través del canal como cuasipartículas (ondas de electrones) con cierta efectiva m*. La conmutación ON/OFF depende de dicha masa efectiva. En un transistor TFET un buen estado ON prefiere una masa efectiva baja, pero un buen estado OFF una grande. Lograr ambas cosas parece imposible, pero un transistor TFET con una puerta de fosforeno en forma de L lo permite (como el mostrado en la figura que abre esta entrada). El lado corto de la L presenta una m* baja y el lado largo de la L una m* alta.

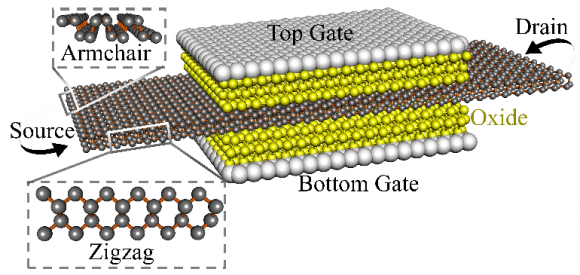

Para el diseño de un buen transistor MOSFET con fosforeno se requiere una masa efectiva m* grande. Por ello se propone el uso de una nanotira (nanoribbon) que en el borde corte presenta la estructura tipo «armchair» del fosforeno y en el lado largo la de «zigzag» del mismo material. Gracias a esta diferencia (que no tienen materiales como el grafeno) se obtienen buenas curvas de conmutación incluso para un canal de 1,6 nm (según las simulaciones por ordenador).

En resumen, el uso de un material con una masa efectiva anisótropa en el canal de un tranistor MOSFET o TFET permite reducir su tamaño hasta 1-2 nm sin degradar en exceso la calidad de la conmutación ON/OFF. Por supuesto, habrá que esperar a que estos resultados sean confirmados en laboratorio. Nadie debe llevarse a engaño. Las técnicas de fabricación actuales no permite fabricar en masa estos dispositivos. Pero quien sabe si en una o dos décadas pueden acabar copando el mercado.

Muy buena entrada Francis, recuerdo que hace tiempo publicaste el nuevo Roadmap de la industria, y la verdad es que se está quedando en nada, porque todo pinta a que la carrera por la integración no se va a detener. Global Foundries tiene FD-SOI a 22 nm en el mercado(disminuyendo el coste de los 28 nm en bullk, en contraposición a los FinFET de 14 nm), Samsung ya está produciendo FinFET a 10 nm (llegarán al mercado a finales de año en productos), y TSMC esta semana ha anunciado que ya está haciendo pruebas con obleas a 7 nm para producción masiva de cara a finales 2017 – 2018. Y todavía no ha llegado EUV; creo que posiblemente se retrasará de año y medio a 2 años o 2 años y medio. Pero la miniaturización y las consiguientes mejoras no se van a detener, ¿con qué nos sorprenderá intel?

Ya se que es muy pronto para hablar de esto pero ¿como anda el tema de la electromigracion a esas escalas?

Y pregunto a un nivel puramente teórico

Interesante cuestión Orbatos, aunque el uso de este tipo de materiales esté muy lejano todavía como señala Francis, quizás si el chip se fabricase de forma íntegra usándolos con un vector J mucho mayor si se pudiese volver a subir la frecuencia para los procesadores. Por otro lado, aunque esto fuese posible, creo recordar que conforme la frecuencia aumenta, el consumo de potencia lo hace prácticamente al cuadrado, por lo que sería interesante ver si se podría subir mucho de frecuencia.

Orbatos, el artículo presenta simulaciones teóricas por ordenador que no tienen en cuenta la electromigración. Así que no puedo contestarte. Solo puedo decirte que, en general, los materiales bidimensionales (grafeno, fosforeno, …) son muy robustos y muy resistentes ante la electromigración.

Interesante noticia, Francis.

Esto me hace pensar un poco:

Pasar de 20 nm a 10 nm (10 nanómetros de diferencia) supone un incremento de la densidad de transistores en un factor de 4; sin embargo pasar de 10 nm a 1 nm (casi también 10 nanómetros de diferencia, realmente 9) supone un incremento en un factor de 100.

Por tanto, si redondeamos la tecnología de 2016 a 22 nm, para llegar a 1 nm estamos hablado de multiplicar la densidad por 484. Dado que la ley de More (en la actualidad) dice que más o menos se duplica la densidad cada 2 años, tenemos ley de moore para unos 15-18 años. Es decir, más o menos hasta 2030.

Saludos.

hola Francis

Piensas que este semiconductor http://www.eetimes.com/document.asp?doc_id=1329663&page_number=2 podra reemplazar a los procesadores actuales para las computadoras personales en unos años?

Alicia, no sé qué decirte, este tipo de tecnología de obleas de carbono (diamante) es buena para dispositivos electromecánicos (MEMS), pero no parece competitiva a la hora de reemplazar a las obleas de silicio, porque su coste es prohibitivo. No creo que en ningún computador personal se llegue a usar esta tecnología. Pero nunca digas nunca jamás. Espero estar equivocado y que ADT (Advanced Diamond Technologies) se convierta en una empresa revolucionaria… pero, sinceramente, no creo que lo logre.

Muchas gracias Francis por todas las primicias!

Viendo que el parámetro de red (si se puede llamar así en redes bidimensionales), es de unos 400pm simplificando a que fuera un cuadrado, me salen de 2,5 a 5 átomos para un puerta de 1-2 nm (alucinante!!) si mis estimaciones no se salen mucho del tiesto. Tendría un par de dudas:

– ¿Se podrán tener puertas estables con +- 2×2 átomos? ¿Cómo leñes conseguirán hacer la litografía?

– ¿Qué pasaría si se usara una sola lámina, en lugar de dos «zizageadas» en el drenaje?

– ¿Por dónde crees que pasará el futuro de la computación una vez se alcance el límite físico en miniaturización?

Muchas gracias de antemano por tu trabajo.

Yavi, recuerda que una «puertas con +/- 2×2 átomos» no significa un dispositivo con pocos átomos, el resto puede ser muy grande (cientos o miles de átomos). Obviamente, la fabricación tendrá que usar una versión futura de la «litografía». Se han propuesto dispositivos tipo transistor con una sola lámina, pero no son similares a MOSFET/TFET, como pretende el nuevo trabajo (que por ahora es teórico y quizás en laboratorio no funcione tan bien). Sobre el futuro tras alcanzar el límite físico de un solo átomo no tengo ni idea por dónde irá… No soy futurólogo, aunque conozco las ideas de Kurzweil, Bostrom y otros futurólogos que proponen la singularidad tecnológica (que la computación acabará usando partículas fundamentales en lugar de átomos).

Hace años se hablaba de la fotónica como nuevo campo para desarrollar una nueva computación, pero parece que se quedó en agua de borrajas. Entre el desarrollo tridimensional de obleas, computación cuántica y el resto de tecnologías que se están investigando, espero poder asistir a la nueva revolución de la computación. ¡Y que nos lo quieras seguir contando, Francis!

LISTO! se veia venir: el grafeno quedó en mucho ruido y pocas nueces, ya vino el fosforeno y lo va a hacer pasar a retiro adelantado

Lo dices así porque no debes leer compulsivamente a francis jejeje

Lo comento porque él lo explicaba muy bien en otra entrada; no vamos a la edad del grafeno, vamos a la de los materiales bidimensionales: https://francis.naukas.com/2015/01/15/materiales-bidimensionales-fosforeno-arseneno-y-antimoneno/

Saludos