El tamaño de un transistor se mide por la longitud de su canal de puerta. Según la física actual, un transistor de silicio no puede tener un canal menor de cinco nanómetros. Para bajar de esta cifra hay que usar otras tecnologías, como los transistores de nanotubos de carbono. Se publica en Science el primer transistor 1D2D-FET con un canal de puerta de solo un nanómetro. La parte 1D del nombre corresponde a un nanotubo de carbono, la parte 2D es una bicapa de disulfuro de molibdeno (MoS2) monoatómico y la parte FET a que el transistor es compatible con la tecnología MOSFET.

Increíble, sin embargo, hay que tener cuidado. La definición de canal de puerta en este tipo de transistores 1D2D-FET es diferente a un transistor MOSFET convencional. No se trata de algo físico que podemos ver al microscopio electrónico. Para estimar la longitud efectiva del canal de puerta hay que usar simulaciones por ordenador. En el estado OFF del transistor 1D2D-FET se estima que el canal tiene ~4 nm y es en el estado ON cuando se alcanza ~1 nm; un titular más riguroso para esta noticia es que se ha logrado un transistor tipo FET con canal de puerta menor de 5 nm.

El artículo es Sujay B. Desai, Surabhi R. Madhvapathy, …, Ali Javey, «MoS2 transistors with 1-nanometer gate lengths,» Science 354: 99-102 (07 Oct 2016), doi: 10.1126/science.aah4698. Recomiendo leer «Smallest Transistor Ever,» Science Bulletin, 07 Oct 2016.

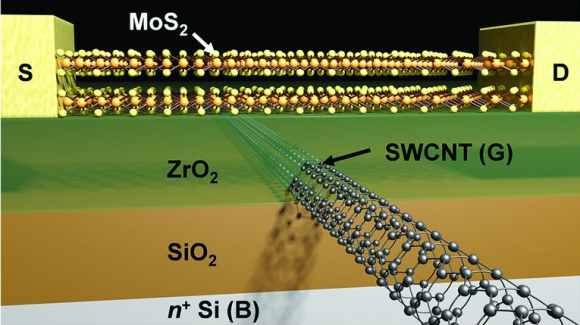

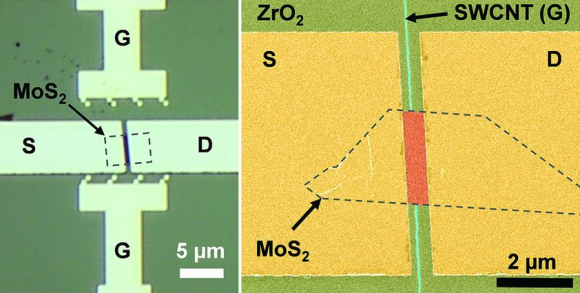

Los transistores 2D-FET fabricados una puerta de MoS2 prometen ser el reemplazo de los transistores de silicio. Sin embargo, no se ha logrado que su canal baje de cinco nanómetros. Por ello, el nuevo artículo ha usando un nanotubo de carbono colocado bajo la puerta para lograr un transistor 1D2D-FET con una puerta de solo un nanómetro. Estas fotografías muestran el diseño del dispositivo, con el canal de puerta entre la fuente (S) y el drenador (D), conectando los dos terminales externos de puerta (G).

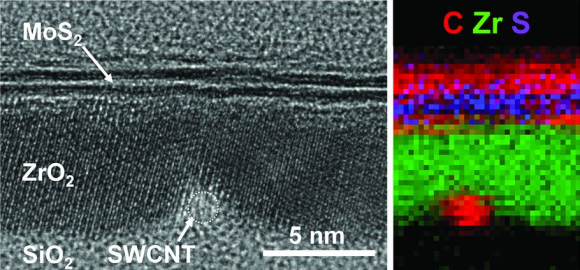

El canal del transistor se encuentra entre el nanotubo de carbono de una sola capa (SWCNT) y varias capas de MoS2 (el canal tiene ~1 nm cuando hay solo dos capas, pero como muestra esta microfotografía el número de capas varía por el proceso de fabricación). El dielétrico usado como puerta es de ZrO2 y el nanotubo de carbono está colocado sobre un sustrato de 50-nm SiO2/Si. La fabricación de este tipo de dispositivos es muy complicada, más próxima al arte que a la tecnología. Con seguridad hay muy pocas personas en el mundo capaces de lograrlo.

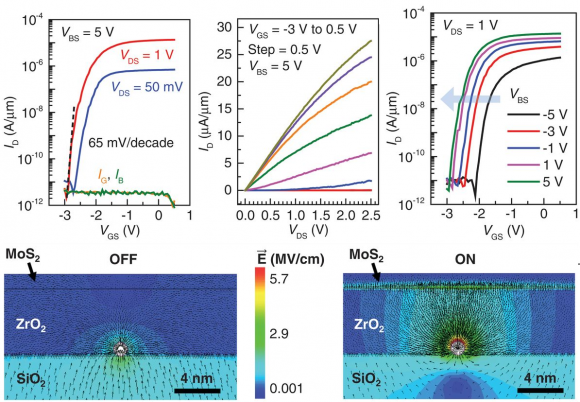

Las características eléctricas del transistor 1D2D-FET son excelentes incluso a temperatura ambiente. Estas figuras muestran las características ID–VDS para diferentes valores de VGS y un valor fijo VBS = 5 V. Quien conozca el funcionamiento de los transistores FET reconocerá dichas curvas fácilmente. La parte de abajo de esta figura muestra las simulaciones por ordenador que permiten estimar la longitud efectiva del canal de puerta en los estados OFF y ON. En el estado OFF se estima LEFF ~ LG = 3,9 nm, y en el estado ON se estima LEFF ~ LG = 1 nm.

Un punto que me gustaría destacar, para que nadie se confunda, es que el transistor completo tiene un tamaño mayor de la longitud del canal. Más aún, en los prototipos fabricados su tamaño es enorme comparado con un transistor de la CPU de tu ordenador. Siendo el canal el elemento clave que limita el tamaño final de integración del transistor se ha buscado que sea inferior a 5 nanómetros. Futuros avances lograrán reducir el tamaño completo del transistor.

Tampoco me gustaría olvidar el gran problema de los transistores 1D-FET con nanotubos de carbono (los primeros prototipos son de 1998). Colocarlo en su sitio es muy difícil con las tecnologías actuales y para su fabricación en masa serán necesarios muchos avances futuros (no veo fácil que se logre en menos de una década, pues en la última década se ha avanzado muy poco). Por tanto, es posible que avances en otras tecnologías conviertan a estos transistores 1D2D-FET en una promesa incumplida. Como es obvio, espero errar en mi predicción.

Hola Francis

Cual de todas las tecnologias crees que reemplazaeran al silicio, en la computadoras personales?

Algo parecido iba a preguntar, el silicio se ha mantenido por muchas décadas y la fantástica especialización a la que ha evolucionado hace difícil que una tecnología fuera del silicio venga a reemplazar nuestros procesadores. y electrónica. ¿se avizora alguna tecnología fuera del silicio que a mediano plazo lo reemplace? existen muchas especulaciones pero no pasan de eso. Meter 1.170 millones de transistores en un chip (Core i7), todos trabajando en conjunto de manera coordinada y a altas velocidades no es nada de trivial.

Cecilia y Rene, ahora mismo es imposible saberlo, porque será la tecnología que menos cambios requiera en la producción industrial; hay una enorme diferencia entre la producción de prototipos en laboratorio y la producción masiva a escala industrial. En mi blog y otras fuentes similares solo hablo de ciencia en laboratorio y prototipos fabricados uno a uno; la tecnología industrial avanza a otro ritmo y publica sus avances a posteriori. Por tanto, predecir qué material sustituirá al silicio más allá de 2025 raya lo imposible.

Se agradece la objetividad en la respuesta.

lo que son los nanotubos de carbono, el grafeno, y la fusión nuclear (lease ITER), son las promesas incumplidas de siempre, son el glorioso futuro que nunca se hace presente

… y la prueba fisica de la teoria de cuerdas…

Gerardo, ya hay aplicaciones comerciales de los nanotubos de carbono (p.ej. hay raquetas de tenis y ruedas de bicicletas que los contienen, y también aplicaciones aeronáuticas). Por ahora todas están basadas en redes no ordenadas de nanotubos (materiales con nanotubos incrustados). Las aplicaciones que usan un solo nanotubo están todavía muy lejos, pues manipular los nanotubos uno a uno es muy costoso. También hay aplicaciones comerciales del grafeno; de nuevo, se trata de redes desordenadas incrustadas en materiales. Luego no se puede afirmar que sus aplicaciones prácticas sean una promesa incumplida. En 2015 el mercado nanotecnológico alcanzó unos 800 000 millones de dólares (quizás te parezca una promesa incumplida que no haya alcanzado el billón de dólares, pues de otra manera no lo entiendo; pero lo logrará en 2016).

Por otro lado, la fusión es un proceso lento, pero seguro, de JET a ITER y de ITER a DEMO. Decir que la fusión es una promesa incumplida es falso. Nadie prometió que JET fuera un prototipo de reactor de fusión comercial. Nunca. El objetivo de JET, lograr Q>1, fue conseguido. Y dudar de que el objetivo de ITER, lograr Q>10, sea conseguido, cuando aún está en construcción, me parece hablar por hablar. Por supuesto, DEMO sigue lejos (su diseño final requiere conocer los resultados de ITER).

Francis en otra nota tu dijiste que el reemplazo del silicio iban a ser las redes de nanotubos de carbono, ya no piensas asi?